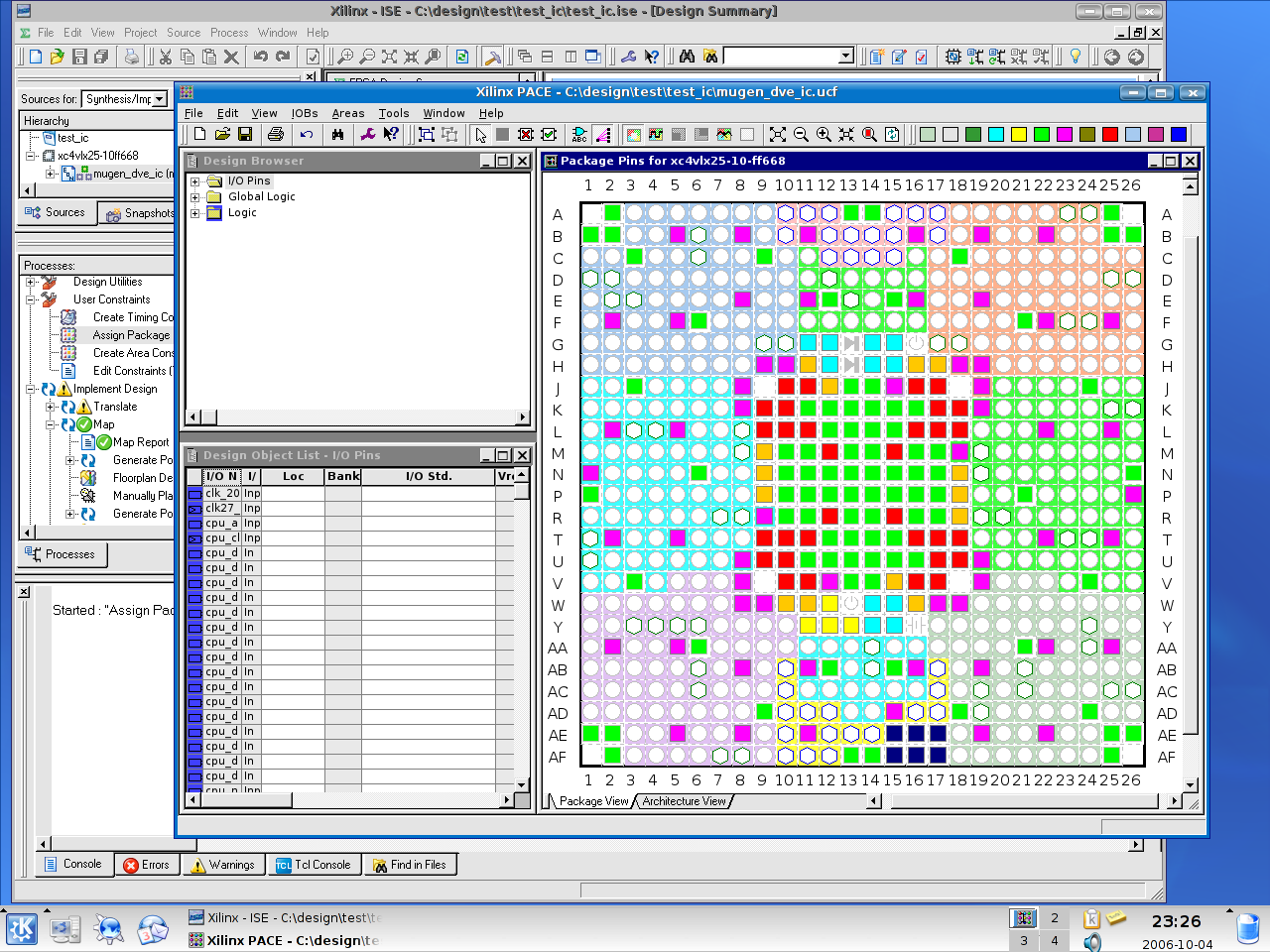

To observe where your signals were mapped onto the FPGA, your can look at the PAD Report. Helpful Tools Associated with Xilinx Project Navigator: In the Processes for Current Source: window there are some utilities and reports that can help you with your design. Now you can demonstrate that your design is properly working. The bit stream will be downloaded onto the XESS XSA-50 FPGA protoboard. Simply drag the *.bit file into the FPGA/CPLD of the GXSLOAD utility.

#Xilinx ise software windows#

Use the My Computer windows feature to go to the subdirectory where your subdirectory you created in step 3 is located. The utility can be found in Start > Engineering Applications > XESS > GXSLOAD or using the following icon: The following application will be started for download. To accomplish this, we must use the XESS GXSLOAD utility.

#Xilinx ise software download#

Now you are ready to download your bit stream onto the XESS XSA-50 FPGA protoboard. Additionally, since the route, place and map procedures done in step 7 mapped I/O without a user constraints file, you may have to repeat step 7 with the user constraints file that you just created. All you do is add the *.ucf file to your design. If you use this file in the future, you do not need to create it as in step 8. In the Xilinx Constraints Editor pull-down menu, select File > Save. Make sure you save the mappings to the *.ucf file that you just created for possible future use. Ensure you enter a P for pin before each pin number. You can enter the I/O to/from your FPGA as being used on the XESS XSA-50 FPGA protoboard. The Xilinx Constraints Editor Window will be displayed. In the Processes For Current Sources: window, double click on the following application: User Constraints > Create Timing Constraints. Make sure you highlight your top-level design in the Sources in Project: window. If you successfully complete this action, there will be check marks to the left of your design name(s) 3ġ0 In the Sources in Project: window the *.ucf file is now added to your design. Repeat step 5, but highlight each component to load its associated VHDL file. If using a hierarchical design, the other files must be added. The high-level ARCHITECTURE is defined in the file counter7segment.vhd. It has an ARCHITECTURE block with two components (counter & leddcd). It should be noted that the example used in this tutorial is a hierarchical design. Xilinx Project Navigator will load your design and the windows will look something similar to what is illustrated below. Make sure VHDL Module is highlighted and press OK. You may be asked to clarify what is the source via the Choose Source Type window. Note if you are using a hierarchical design, enter the high level module first.

#Xilinx ise software code#

Now enter your source code through the Add Existing Sources window by highlighting the desired source code and pressing Open. Using the pull-down menu (or alternatively the right mouse click) select Project > Add Source. In the Sources in Project window, left click on the line where XC2s50 5tq144-XST VHDL (or XC2s50 6tq144-XST) is located to highlight that entry. Next you need to add your source code to the project. At this point you should make sure your already compiled and simulated VHDL source code is located in the directory you created in step 3. After starting the Xilinx Project Navigator, the following screen will be displayed: 1ģ 5. To Start the Xilinx Project Navigator, Start > Engineering Applications > Xilinx ISE 5 > Project Navigator or using the following icon: 2. Assumption: Students have a basic understanding of Windows Procedures: 1. Finally, although the downloading utility is NOT apart of the Xilinx Project Navigator, the steps to download the design are also provided here. Generate a bit stream so the design can be downloaded onto the Spartan II FPGA residing on the XESS XSA-50 FPGA protoboard. Sendek Xilinx Project Navigator Reference Guide Background: This guide provides you with step-by-step procedures in using the Xilinx Project Navigator to perform the following: Synthesize your Very High speed Integrated Circuit Hardware Description Language (VHDL) code to a netlist Map, place and route your netlist onto a Spartan II FPGA (which is used on the XESS XSA-50 Field Programmable Gate Array (FPGA) protoboard Map Input/Output (I/O) pins to devices on the XESS XSA-50 FPGA protoboard.

0 kommentar(er)

0 kommentar(er)